# Testing and remote access to embedded system DPI/LVDS display output

Marek Vasut

June 28th, 2023

#### Table of content

- Motivation and why own hardware

- Display busses and capture options

- Approaches to the problem at hand

- Hardware build and testing

- ► LVDS encore

- ► Wrap up

#### Marek Vasut

- U-Boot bootloader custodian

- ► Linux kernel developer

- ► OE contributor

- ► FPGA hobbyist

- Consultant

#### Motivation

- SoM vendor development kit panel (re)testing

- Too many panel options for each development kit

- ► Testing them all means constant unplugging and replugging

- Eventually the connector fails ...

- Remote access

- Sometimes it is not viable to ship hardware

- Hardware in limited quantity or early prototype stage ...

- Sometimes it is convenient to put the hardware in rack and use remote access from anywhere

- CI testing

- Automated SoM IO test in production is a must

- Automated test of all available panels on each update is great

- Automated testing improves confidence in release quality

Need Device which is plugged in once and can do all of the above.

#### Available options

- ► Grab fbdev content and stream it over e.g. ethernet

- cons f1 Does not work (well) with modern DRM subsystem (fbdev is deprecated for over a decade)

- cons f2 A fully assembled frame buffer may not even exist in DRAM

- cons f3 Does not provide any information about the situation past the video buffer in DRAM (CRTC/BRIDGE(s)/CONNECTOR(s)), i.e. the pixels which are sent to the panel itself

- Weston RDP backend

cons w1 Overhead of assembling and payloading buffers to RDP stream cons w2 Same as f3 above, no information past DRAM buffer

- DRM subsystem CRTC CRC support

- CRTC on some SoCs is capable of returning CRC of currently scanned out frame

- Used for functional safety reasons (e.g. in automotive)

- Used by [igt-gpu-tools] for CI testing

- cons c1 No full image available for inspection/remote access

- cons c2 Similar to f3 above, no information past CRTC output

Need Capture the whole display output of the device.

## Embedded systems display busses

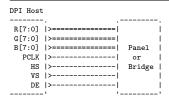

#### DPI Display Parallel Interface

- Likely oldest and simplest of still used interfaces

- ► Clock line, 1..24+ data lines, HS/VS/DE sync signals

- Wild source to sink data line mapping

- Uses LVTTL 3V3 signalling

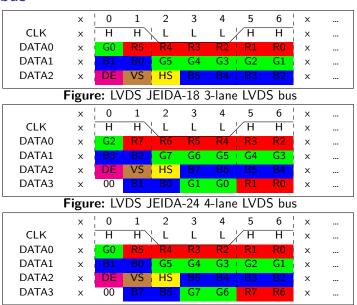

#### FPD Flat Panel Display Link

- Uses LVDS Low-Voltage Differential Signaling

- ▶ 1 differential clock lane + 3/4 differential data lanes

- Often incorrectly called LVDS

- ► FPD-Link is ≈ serialization of DPI

- Fewer available bus formats (1x 18bit and 2x 24bit)

#### DSI MIPI Display Serial Interface

- Entirely different from the above

- MIPI Alliance standard

- ▶ Differential signaling, multiple PHYs, HS/LP mode

- Packet based protocol with back channel

#### DPI bus

- Clock, data, HS, VS, DE signals

- Closely matches panel behavior

- Maximum clock rate limited by too many data lines

- Often found in older panels

- Signal polarity and sampling edge is important

- Different modes HS/VS or DE

- Widely varying pixel formats

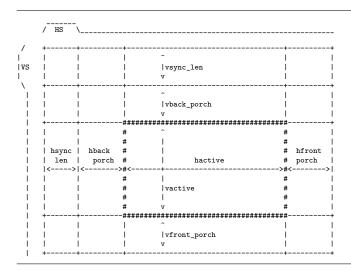

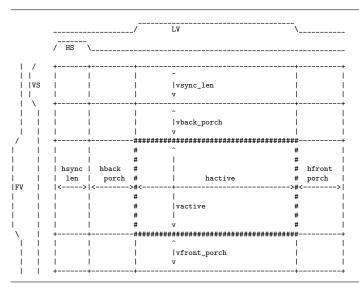

## DPI timing and synchronization

Linux 6.4-rc6 [Documentation/devicetree/bindings/display/panel/panel-timing.yaml]

#### DPI capture

- ▶ What should the device capture ?

- ► Active area only fewer data, but incomplete

- Everything including margins great for CI test

- ▶ DPI panel maximum resolution  $\approx 1024$ x600 24bpp 60FPS

- Sampling other interesting signals

- Use signals above the 24bpp

- Capture 32bpp instead

- ► Interesting signals include HS/VS/DE and even PWM...

- ▶ Data rate at 1024×600 32bpp 60 FPS including margins

- ► Lets assume CDTech S070PWS19HP-FC21 panel

- ► Total width W(pixels) = HSA + HBP + HACT + HFP = 20 + 140 + 1024 + 160 = 1344

- ► Total height H(lines) = VSA + VBP + VACT + VFP = 3 + 20 + 600 + 12 = 635

- Total data rate  $D = W * H * (32bpp/8) * 60FPS \approx 204MiB/s$

- ightharpoonup Data rate at 1920x1080 32bpp 60 FPS  $\approx 500 MiB/s$

Need high bandwidth interface

## CDTech S070PWS19HP-FC21 panel timing

## Linux 6.4-rc6 [drivers/gpu/drm/panel/panel-simple.c L1263]

## High bandwidth interfaces

What is available on most PCs and can receive high bandwidth continuous stream of data?

```

Ethernet Gigabit

pro Almost every PC has gigabit ethernet plug

con Insufficient bandwidth of \approx 125 MiB/s

Ethernet Multiple bonded gigabit ethernets

con Too complex

Ethernet 10G ethernet

con Seldom available on contemporary PCs

con Complex and expensive on FPGA TX side

USB 2.0

pro Almost every PC has USB 2.0 plug

con Insufficient bandwidth of \approx 60 MiB/s

Compression might help, but not useful for testing and CI

USB 3.0

pro Almost every PC has USB 3.0 plug

pro Enough bandwidth on root port of \approx 625 MiB/s

Need to use USB 3.0 and avoid any downstream hubs

```

## 32bit input to USB 3.0 bridge chips

Existing 32bit-input-to-USB3.0 bridge chips:

#### FTDI FT602Q

- ▶ 32bit RX FIFO to USB 3.0 UVC (USB Video Class) device

- pro No need for firmware

- pro USB UVC device, behaves like a webcam

- con FT602Q is 100MHz or 66MHz clock source

- con Need asynchronous FIFO between DPI⇔FT602Q

#### Cypress FX3

- ▶ 32bit general purpose interface, CPU, DMA, USB 3.0 device

- pro Flexible due to CPU and 32bit up to 100 MHz GP interface

- pro GP interface does support external clock input

- pro Familiar ARM926EJS ARMv5 core

- pro Documentation for the chip peripherals is good

- pro Firmware examples contain CPI camera to UVC video demo

- con CPI to UVC demo must be adapted and pixel format tweaked

- Not all of vendor firmware SDK runs on Linux

- Vendor firmware SDK is dubiously licensed outdated blobware

## Multiple approaches

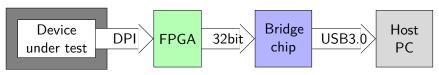

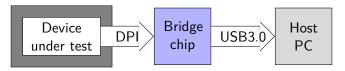

- ▶ DPI→FPGA→bridge as UVC→Host PC

- Maximum compatibility

- ▶ Native USB UVC support in most OSes (not enough)

- FPGA adds to price and complexity

- ► FX3 as UVC requires blobware firmware

- FX3 input state machine design tool does not work on Linux

- ▶ DPI→bridge as FIFO→Host PC

- Maximum simplicity

- Requires custom host software (easy)

- Read data from bridge

- Display / write to file / pass to e.g. gstreamer

#### Failed UVC blobwork

#### Multiple problems:

- 1. UVC USB Video Class does not support varying resolution

- 2. Both FT602Q and FX3 in UVC mode expect CPI sensor input

## UVC pixel format inflexibility

- USB UVC is USB-IF (Implementers Forum) standard

- Stream width, height, pixel format, bitrate, ... all encoded in static USB descriptors

- Not all pixel formats supported by various OSes are part of the USB-IF standard

- Some pixel formats are non-standard extensions, usually poorly documented

- ▶ BGRX8888 extension pixel format now in Linux 6.1.y media: uvcvideo: Add GUID for BGRA/X 8:8:8:8

- Cypress firmware can be patched to produce this format

- As far as I can tell, patch cannot be distributed due to SDK licensing

## **UVC** resolution inflexibility

- UVC USB Video Class does not support changing resolution during streaming

- The DPI input resolution may change at runtime or even fluctuate (during debugging)

- Linux kernel uvcvideo driver expects continuous stream

- Linux kernel uvcvideo driver checks line width

- Frames with short lines dropped without module parameter: uvcvideo nodrop=1

- Both gstreamer and ffmpeg check V4L2 frame size

- Short frames are dropped unless either is patched

- This is not really seamless experience

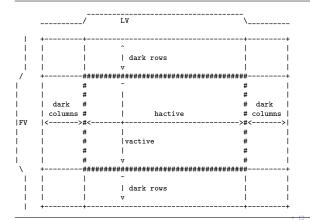

## CPI timing and synchronization

- CPI uses two sync signals to denote active area with valid pixels

- LV Line Valid Indicates active columns ( $\approx HFP + HSA + HBP$ )

- FV Frame Valid Indicates valid rows ( $\approx VFP + VSA + VBP$ )

- ► Example: MT9P006 Pixel Array Structure + LV and FV

## CPI vs. DPI timing

Need adapter which converts DPI sync signals to CPI sync signals

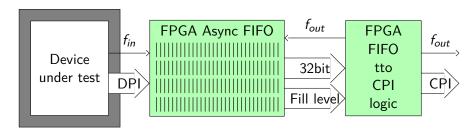

#### FPGA asynchronous FIFO

- Crossing clock domains with an Asynchronous FIFO The ZipCPU by Gisselquist Technology

- ► A FIFO used to move wider data from one clock domain to another

- ▶ Width and depth often configurable

## FPGA asynchronous FIFO implementation

- ightharpoonup Assume  $f_{in} < f_{out}$

- Assume FIFO width is 32 bits and depth is slightly more than 1 full line worth of pixels

- ► FIFO fill level ≈ LV

- ▶ When FIFO contains 1 line worth of input data, it can be flushed into the output bridge

- Padding to the width configured in the UVC descriptors is necessary

- Line counting to emulate FV is necessary

- ► The FV can be a short pulse (not a full line) for FX3 to recognize it

- ► If FIFO output does not produce data for too long ⇒ this is loss of signal

- ► FIFO must be carefully placed in FPGA and timing constraints are a much

- ▶ Altera Cyclone IV/E maxed out at  $f_{out} \approx 65 \ \mathrm{MHz}$

#### Failed UVC blobwork is failed

#### Summary:

- UVC was not a win due to necessary workarounds

- ► Firmware patching was extremely problematic

- DPI to CPI adapter using FPGA is convoluted

## Success with bridge as FIFO

- ▶ FTDI FT601Q is 32bit FIFO to USB 3.0, but still clock source

- Cypress FX3 is capable of being a clock sink

- Capture raw byte stream using FX3, process on Host PC

- ► The FX3 firmware and tooling is still a problem

- The vendor tooling is a problem

#### sigrok

- sigrok project The sigrok project aims at creating a portable, cross-platform, Free/Libre/Open-Source signal analysis software suite that supports various device types (e.g. logic analyzers, oscilloscopes, and many more).

- ► fx2lafw fx2lafw is an open-source firmware for Cypress FX2 chips which makes them usable as simple logic analyzer and/or oscilloscope hardware.

If only there was similar firmware for Cypress FX3.

#### fx3lafw

- fx3lafw [link] by Marcus Comstedt This is an open source firmware for using a Cypress FX3 USB controller as a logic analyzer with sigrok. It does not rely on any libraries or tools provided by Cypress under license.

- Suggested by t4nk at sigrok channel during unrelated discussion – THANK YOU!

- No need to use the Cypress blobware anymore

- Compatible with fx2lafw with extension to support faster sampling

- Uses clock generated by FX3 to oversample the 32bit bus

- sigrok support is implemented by a few easy patches to libsigrok [link], currently outdated, but rebase is easy

## What is missing

- Switch the fx3lafw to use external clock from DPI

- Capture data using sigrok and pipe them into e.g. gstreamer

- Replace sigrok with something more lightweight

- Build more permanent hardware setup

## Patching fx3lafw

- Clock direction bit must be flipped

- SYNC/SPEED bits must be enabled

Needed for higher speed capture and capture synchronous to input PCLK

- DLL must be disabled else slight data loss happens

Resulting image crawls slowly to the left and wraps around

- Input PCLK invert configuration (for selection of PCLK sampling edge) is a good tunable to have, implemented using libusb control endpoint, like other fx2lafw configuration messages

- ► Use libusb fxload example tool to load firmware into FX3 (or run sigrok-cli twice, the first time will fail to re-enumerate the FX3 as it changed bus from USB 2.0 to USB 3.0 and libsigrok cannot handle that yet)

- ► Patched fx3lafw [link]

#### Build and use fx3lafw

```

# Udev rule (use 'udevadm control -R' to reload the rules once added)

$ cat /etc/udev/rules.d/92-cypress.rules

SUBSYSTEM=="usb", ATTRS{idVendor}=="04b4", ATTRS{idProduct}=="00f3", MODE="0666"

fx3lafw $ git clean -fqdx

fx3lafw $ make -j$(nproc)

# For stgrok purposes

fx3lafw $ cp fx3lafw-cypress-fx3.fw /usr/share/sigrok-firmware/

# For libusb/faload purposes

fx3lafw $ cp -Lv fx3lafw-cypress-fx3.fw fx3lafw-cypress-fx3.img

fx3lafw $ /libusb/examples/fxload -t fx3 -i fx3lafw-cypress-fx3.img

```

#### sigrok continuous capture

- ► The sigrok-cli tool supports triggering capture from command line

- Captured data can be stored into a file in different formats:

- -0 binary or -0 csv ...

- ► Capture into file is useful for detailed analysis

- ▶ The file can be a named pipe (FIFO) for realtime visualization

- FIFO needs a consumer too

- sigrok supports software triggers -t channel, useful to trigger on edge of sync signal(s)

- ► **Gerhard Sittig** of sigrok fame suggests --continuous option

```

$ mkfifo /tmp/fifo

```

<sup>\$</sup> sigrok-cli -D -d fx2lafw --continuous --channels \

D0,D1,D2,D3,D4,D5,D6,D7,D8,D9,D10,D11,D12,D13,D14,D15,D16,\

D17,D18,D19,D20,D21,D22,D23,D24,D25,D26,D27,D28,D29,D30,D31 \

-t D24=r --config samplerate=192m -1 5 -o /tmp/fifo -0 binary

<sup>4□ &</sup>gt; 4□ > 4□ > 4□ > 4□ > 900

#### Gstreamer FIFO consumer

- ► The last step is to create FIFO consumer that can visualize the data

- Gstreamer is a good candidate with gst-launch-1.0 tool

- Easily assemble a pipeline

- ► It is necessary to know the input stream resolution, otherwise the visualization will be distorted

- ► Lets assume CDTech S070PWS19HP-FC21 panel again 1024x600 active area, 1344x635 including margins

```

$ W=1344 H=635 S=$((4*$W*$H)); gst-launch-1.0 \

filesrc location=/tmp/fifo blocksize=${S} ! \

video/x-raw,width=${W},height=${H},framerate=60/1,format=RGBx ! \

queue ! \

videoconvert ! \

autovideosink

```

## Replacing the RX with light weight tool

- ► A more light-weight tool called fx3stream is available at [link]

- Based on libusb with optional xlib and gstreamer dependencies

- ► The tool is currently rudimentary

- ▶ Provides three sink options FIFO, Gstreamer, X11 window

- Gstreamer sink is an appsink which push feeds gstreamer pipeline

- Provides frame rate counter (using gstreamer fpsdisplaysink)

- Provides sync signals visualization

- Compile, upload fx3lafw to FX3 using fxload, run the tool

## Demo – Linux is booting

- Chefree CH1010LHLWH-002 1280x800 panel connected via DPI-to-LVDS bridge. The capture is attached to the DPI, i.e. before the DPI-to-LVDS bridge.

- ► Host: \$ ./stream-gst 1440 823 0 0 0

```

2.970011] inx-drm displau-subsustem: bound inx-ipuu3-crtc.3 (ops 0xc0b5b744

2.9774311 inx-drm displau-subsustem: bound inx-ipuo3-crtc.6 (ops 0xc0b5b744

2.9848151 inx-drm displau-subsustem: bound inx-ipuo3-crtc.7 (ops 0xc0b5b744

2.9921931 inx-drm displau-subsustem; bound disp0 (ops 0xc0b5b9c0)

2.998992] [drm] Initialized inx-drm 1.0.0 20120507 for display-subsystem on

3.0190321 random: crng init done

3.2472581 Console: switching to colour frame buffer device 160x50

3.2699881 inx-drm display-subsystem: [drml fb0: inx-drmdrmfb frame buffer device

3.2843461 etnaviv etnaviv: bound 130000.gpu (ops 0xc0b6881c)

3.2905131 etnaviv etnaviv: bound 134000.gpu (ops 0xc0b6881c)

3.2966861 etnaviv etnaviv: bound 2204000.gpu (ops 0xc0b6881c)

3.3027251 etnaviv-gpu 130000.gpu: model: GC2000, revision: 5108

3.3091701 etnaviv-gpu 134000.gpu; model: GC320, revision: 5007

3.3153631 etnaviv-gpu 2204000.gpu; model: GC355, revision: 1215

3.321573] etnaviv-gps 2204000.gps: Ignoring GPU with UG and FE2.0

3.328333] [drm] Initialized etnaviv 1.3.0 20151214 for etnaviv on minor 1

3.3398961 using random self ethernet address

3.344421 using random host ethernet address

3.3494301 usb0: HOST MAC 76:2e:bd:d5:ee:75

3.3537961 usb0: MAC 42:37:6c:92:11:71

3.3577491 using random self ethernet address

3.3622821 using random host ethernet address

3.3691201 g_ether gadget.0: Ethernet Gadget, version: Memorial Day 2008

3.3702441 g_ether gadget.0: g_ether ready

3.3666731 inx_usb_2184200.usb: No over current polarity defined

3.3993381 ci_hdrc ci_hdrc.1: EHCI Host Controller

3.4065941 ci hdrc ci hdrc.1: new USB bus registered, assigned bus number 1

3.4306771 ci_hdrc ci_hdrc.1: USB 2.0 started, EHCI 1.00

3.4392341 hub 1-0:1.0: USB hub found

3.445405] hub 1-0:1.0: 1 port detected 3.454909] inx thermal 20c0000 anatop:tempon: Automotive CPU temperature grade - max:125C critical:120C passive:115C

3.470344] ALSA device list:

3.4784231 No soundcards found.

3.5192681 EXT4-fs (mmcblkip1): mounted filesystem with ordered data mode. Quota mode: disabled.

3.5246021 VPS: Mounted root (ext4 filesusten) on device 179:1.

3.5371381 deutnpfs: mounted

3.548214) Freeing umused kernel image (initmen) memory: 1024K

3.557512] Run /sbin/init as init process

3.9324321 sustend[1]: Susten time before build time, advancing clock.

```

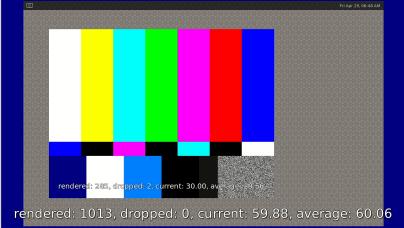

## Demo – Linux, FPS overlay

► Host: \$ GSTFPS=1 ./stream-gst 1440 823 0 0 0

```

9807781 inx-dra display-subsusten; bound inx-inuu3-cetc.7 (ons 0xc0b5b744

2.9881761 inx-drm display-subsystem: bound disp0 (ops 0xc0b5b9c0)

[ 2.994941] [drn] Initialized inx-drn 1.0.0 20120507 for display-subsystem on

3.0165151 random: crng init done

3.2450231 Console: switching to colour frame buffer device 160x50

3.2677561 inx-drm display-subsystem: [drml fb0: inx-drmdrmfb frame buffer device

3.2821811 etnaviv etnaviv: bound 130000.gpu (ops 0xc0b6881c)

3.2883671 etnaviv etnaviv: bound 134000.gpu (ops 0xc0b6881c)

3.2945251 etnaviv etnaviv: bound 2204000.gpu (ops 0xc0b6881c)

3.3005661 etnaviv-quu 130000.quu: model: GC2000, revision: 5108

3.307018] etnaviv-gpu 134000.gpu: model: GC320, revision: 5007

3.3132091 etnaviv-gpu 2204000.gpu: model: GC355, revision: 1215

3.319418] etnaulu-gpu 2204000.gpu: Ignoring GPU with UG and FE2.0

3.326147] [drn] Initialized etnaulu 1.3.0 20151214 for etnaulu on minor 1

3.3377131 using random self ethernet address

3.3422591 using random host ethernet address

3.3472481 usb0: HOST MAC 1a:7d:ae:bb:7e:70

3.3516161 usb0: MAC 6a:36:26:f8:09:15

3.3555711 using random self ethernet address

3.3601041 using random host ethernet address

3.3670091 g_ether gadget.0: Ethernet Gadget, version: Memorial Bay 2008

3.3762161 g_ether gadget.0: g_ether ready

3.3848631 inx_usb 2184200.usb: No over current polarity defined

3.397383] ci hdrc ci hdrc.1: EHCI Host Controller

3.4046971 ci_hdrc ci_hdrc.1: new USB bus registered, assigned bus number 1

3.4280601 ci hdrc ci hdrc.1: USB 2.0 started, EHCI 1.00

3.4365961 hub 1-0:1.0: USB hub found

3.4427831 hub 1-0:1.0: 1 port detected

3.4523941 inx_thernal 20c8900.anatop:tempmon: Automotive CPU temperature grade - max:125C critical:120C passive:115C

3.4675981 ALSA device list:

3 4233941 No soundcards found

3.5656751 EXT4-fs (nuclikini): mounted filesustem with ordered data mode. Quota mode: disabled.

3.5197151 UFS: Mounted root (ext4 filesystem) on device 179:25.

3.5323991 deutnpfs: mounted

3.5435131 Freeing unused kernel inage (initnen) memory: 1024K

3.5527631 Bun /sbin/init as init process

3.9276121 systemd[1]: System time before build time, advancing clock.

```

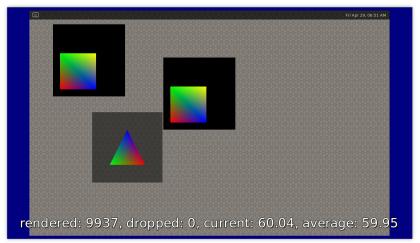

## Demo - Linux, Sync signals visualization and FPS

- Great for CI and debugging purposes.

- Device: weston-simple-dmabuf-egl & weston-simple-dmabuf-egl & weston-simple-egl

- ► Host: \$ GSTFPS=1 ./stream-gst 1440 823 0 0 2

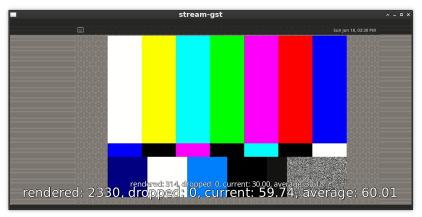

#### Demo - Weston, with FPS, with FPS

- Device: gst-launch-1.0 videotestsrc !

video/x-raw,width=800,height=600 ! queue !

fpsdisplaysink video-sink=autovideosink

- ► Host: \$ GSTFPS=1 ./stream-gst 1440 823 0 0 2

## Loss of signal handling

- ▶ The FX3 expects continuous PCLK input

- Loss of signal triggers GPIF PIB interrupt and stop of capture

- Patch out that interrupt generation

- The FX3 also contains clock loss detection interrupt

- ► Test the clock loss interrupt generation, it does work

- With patched out GPIF PIB stop interrupt, clock loss interrupt is not needed

- ► FX3 is not sending any data on clock loss, and recovers when clock are back

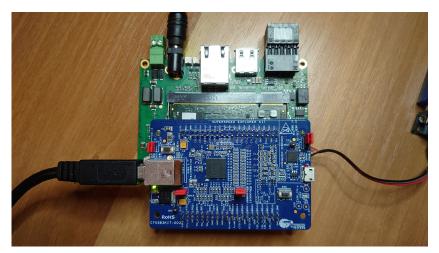

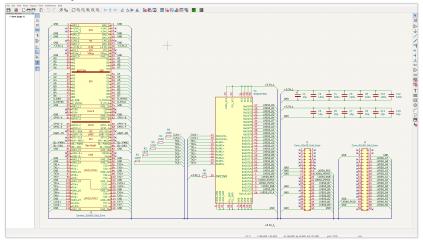

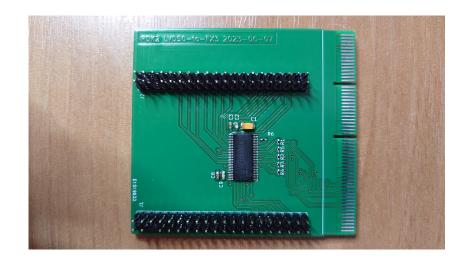

#### Hardware

- ► The Cypress CYUSB3KIT-003 is convenient

- ▶ It provides two 2x20 2.54mm plus spaced 41.5mm apart

- ▶ It is possible to use easy to get 2.54mm M-x cables

- With fly wiring, higher clock frequencies are a problem

- Making permanent hardware connection is a matter of trivial adapter PCB

- Trivial adapter PCB can be designed in KiCad and manufactured at PCB house

- ▶ PCB houses these days can do a lot for you, even populate the PCB ...

- ▶ Make sure you check your newly populated PCB for shorts ...

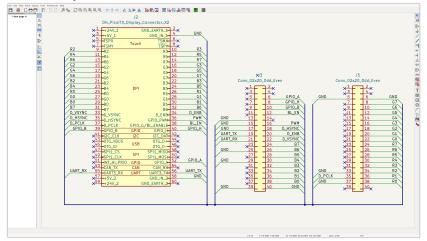

# KiCad - Adapter board schematic

#### Make sure you run ERC

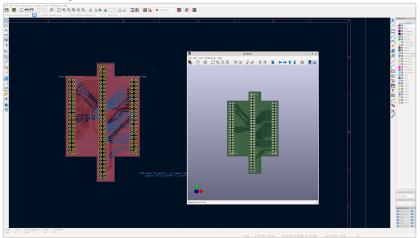

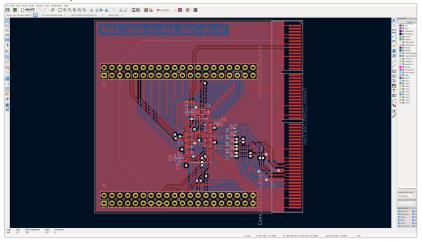

# KiCad – Adapter board PCB

### Make sure you run DRC

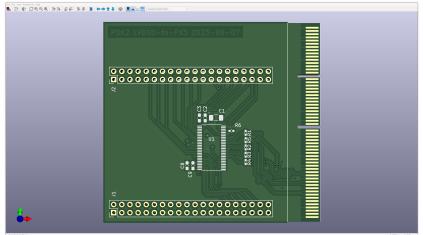

# KiCad – Entire assembly

Stream from the device looks as expected, no surprises there.

### LVDS bus

- Basically a serialization of DPI bus

- ANSI/TIA/EIA-644-A

- Pixel format limited to three options:

- ▶ jeida-18 (SPWG, LDI, VESA)

- jeida-24 (DSIM, LDI)

- vesa-24 (VESA)

- Differential signalling, 1 clock lane, 3 or 4 data lanes

- High resolution panels often use dual-link LVDS

#### LVDS bus

Figure: LVDS VESA-24 4-lane LVDS bus

### LVDS to DPI

- LVDS to DPI deserializer chips do exist

- ► For example TI DS90CF384, OnSemi FIN3386, Thine THC63LVDF84B ...

- Use one of the chips and convert LVDS problem to already solved DPI problem

- Use capacitors close to the chip supplies

- Carefully route LVDS differential lines

- ▶ LVDS lines require  $100\Omega$  termination

### Dual-link LVDS

- Uses 8 differential pairs, transmits 2 pixels at a time

- ► Used to drive 1920×1080 FullHD panels where single-link LVDS does not suffice

- Pixels always sent as odd-even pixel pair

- Likely can be captured using TI DS90CF388 de-serializer and two FX3

- Pixel reassembly on Host PC, possibly using Gstreamer ORC SIMD

## Demo – Linux is booting

- Lets assume EDT ETML0700Y5DHA panel

- ► Host: \$ ./stream-gst 1344 635 0 1 0

```

stream-gst

0.0000001 Rude variant of Tasks RCU enabled

0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 25 jiffies

0.0000001 NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0

0.0000001 GICu3: GIC: Using split EDI/Deactivate mode

0.0000001 GICu3: 160 SPIs implemented

0.0000001 GICu3: 0 Extended SPIs implemented

0.000000] Root IRQ handler: gic_handle_irq

0.0000001 GICu3: GICu3 features: 16 PPIs

0.0000001 GICu3: CPU0: found redistributor 0 region 0:0x0000000038880000

0.0000001 ITS: No ITS available, not enabling LPIs

0.0000001 rcu: srcu_init: Setting srcu_struct sizes based on contention

0.000000] arch_timer: cp15 timer(s) running at 8.00MHz (phys)

0.0000001 clocksource: arch_sys_counter: mask: 0xffffffffffff max_cycles: 0xid854df40, max_idle_ms: 440795202120 ms 0.0000001 sched clock: 56 bits at 8MHz, resolution 125ms, uraps every 2199023255500ms

0.0004201 Console: colour dummy device 80x25

0.000463] Calibrating delay loop (skipped), value calculated using timer frequency.. 16.00 BogoMIPS (lp.j=32000) 0.000479] pid_max: default: 32768 minimum: 301

0.0005741 LSM: Security Francwork initializing

0.6006831 Mount-cache hash table entries: 8192 (order: 4, 65536 bytes, linear)

0.0007021 Mountpoint-cache hash table entries: 8192 (order: 4, 65536 bytes, linear)

0.0023581 cblist_init_generic: Setting adjustable number of callback queues.

0.0023701 cblist_init_generic: Setting shift to Z and lim to 1.

0.0025921 rcu: Hierarchical SRCU implementation.

0.6625981 rcu: Max phase no-delay instances is 1600.

0.0039001 smp: Bringing up secondary CPUs ..

0.6045931 Detected VIPT I-cache on CPU1

0.0046711 GICu3: CPU1: found redistributor 1 region 0:0x00000000388a0000

0.004702] CPU1: Booted secondary processor 0x0000000001 [0x410fd034]

0.0053731 Detected VIPT I-cache on CPUZ

0.0054391 GICu3: CPUZ: found redistributor 2 region 0:0x000000000388c0000

```

## Demo – Linux, FPS overlay

▶ Host: \$ GSTFPS=1 ./stream-gst 1344 635 0 1 0

```

stream-ast

0.0000001 Rude variant of Tasks RCU enabled

9.9999991 rcu: BCH calculated value of scheduler-enlistment delaw is 25 liffies

0.0000001 NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0

0.0000001 GICu3: GIC: Using split EUI/Deactivate mode

0.0000001 GICu3: 160 SPIs implemented

0.0000001 GICu3: 0 Extended SPIs implemented

0.000000] Root IRQ handler: gic_handle_irq

0.0000001 GICu3: GICu3 features: 16 PPIs

0.000000] GICu3: CPU0: found redistributor 0 region 0:0x0000000038880000

0.0000001 ITS: No ITS available, not enabling LPIs

0.000000] rcu: srcu_init: Setting srcu_struct sizes based on contention

0.0000001 arch_timer: cp15 timer(s) running at 8.00MHz (phys)

0.0000001 clocksource: arch sus counter: mask: 0xffffffffffff max cucles: 0xid854df40, max idle ns: 440795202120 ns

0.600000] sched clock: 56 bits at 8MHz, resolution 125ns, wraps every 2199023255500ns

8.8884281 Console: colour dummy device 80v25

0.0004631 Calibrating delay loop (skipped), value calculated using timer frequency.. 16.00 BogoMIPS (lp.j=32000)

0.6004791 pid max: default: 32768 minimum: 301

0.0005741 LSM: Security Framework initializing

0.6006831 Mount-cache hash table entries: 8192 (order: 4, 65536 bytes, linear)

0.0007021 Mountpoint-cache hash table entries: 8192 (order: 4, 65536 bytes, linear)

0.0023581 cblist_init_generic: Setting adjustable number of callback queues.

0.0023701 cblist init generic: Setting shift to Z and lim to 1.

0.002592] rcu: Hierarchical SRCU implementation.

0.0025981 rcu:

Max phase no-delay instances is 1000

0.0039001 smp: Bringing up secondary CPUs

0.0035001 Detected VIPT I-cache on CPU1

0.0046711 GICu3: CPU1: found redistributor 1 region 0:0x00000000388a0000

rendered: 892; dropped: 0,0 current: 64.70, average: 60.04

```

## Demo - Linux, Sync signals visualization and FPS

- Great for CI and debugging purposes

- ► Host: \$ GSTFPS=1 ./stream-gst 1344 635 0 1 2

## Demo - Weston, with FPS, with FPS

- ► Host: \$ GSTFPS=1 ./stream-gst 1344 635 0 1 2

- ► The image stretch left and right is CRTC leaving the data lines in pre-sync state during sync period instead of setting them to zero

# KiCad – Adapter board schematic

#### Make sure you run ERC

It is a really good idea to learn KiCad key bindings (it is faster)

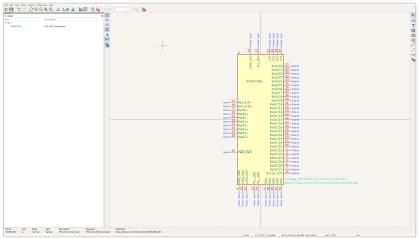

## KiCad – Schematic symbol design

LVDS de-serializer schematic symbols may not be in the KiCad library

Derive symbol from existing high quality symbols in the library

# KiCad – Adapter board PCB

#### Make sure you run DRC

### KiCad - 3D view

Soldering TSSOP56 package at home takes practice and patience Same for 0402 passive components like resistors, don't inhale them

Get a good flux, soldering iron, fume extractor, maybe a loupe ...

# KiCad - Populated board

# KiCad – Entire assembly

Stream from the device looks as expected, no surprises there.

## Next steps - MIPI DSI

- Packet based

- Multiple different PHY options (C-PHY/D-PHY/M-PHY)

- Likely target D-PHY as it is most common in embedded

- ▶ Would require FPGA PHY  $\approx$  HS/LP RX, byte aligner, depacketizer

- HS/LP input into FPGA can be implemented using a few termination resistors and suitable FPGA with the right IO voltage on the right banks

- Multiple FPGA CSI-2 D-PHY RX exists already:

- CircuitValley [link]

- gatecat [link]

- Extracted packets can be fed into FX3 and captured on PC

- ▶ sigrok protocol decoder support might be useful here too

# Wrap up

- ► Hardware is obtainable FX3 kit and adapter board

- ► Software is available

- ► Build is easy

# Thank you for your attention

Questions?

Marek Vasut <marek.vasut+eoss23@mailbox.org>