# Preparing to tape out a fully open J-Core SoC on fully open tools

Rob W. Landley, D. Jeff Dionne Feb 2022

# 0. Background

- J-Core is a patent free, Open Hardware implementation of the SuperH ISA

- SHCompact is a highly optimized ISA targeting high level languages

- The fundamental patents on the 16bit ISA encoding used in ARM Thumb

- Reportedly best selling CPU core in 1990s for 3 years.

- J-Core family is SHCompact+, with SMP extensions for FPGA and ASICs

- Runs Linux right out of the box, much more efficient ISA than RISC-V

- SoC support in mainline Linux since 1996, well tested

#### Roadmap: What comes out from this talk?

- Upward compatible processor family:

- →J0: a 16 bit datapath, 15k ASIC gates (target). 3 stage pipeline

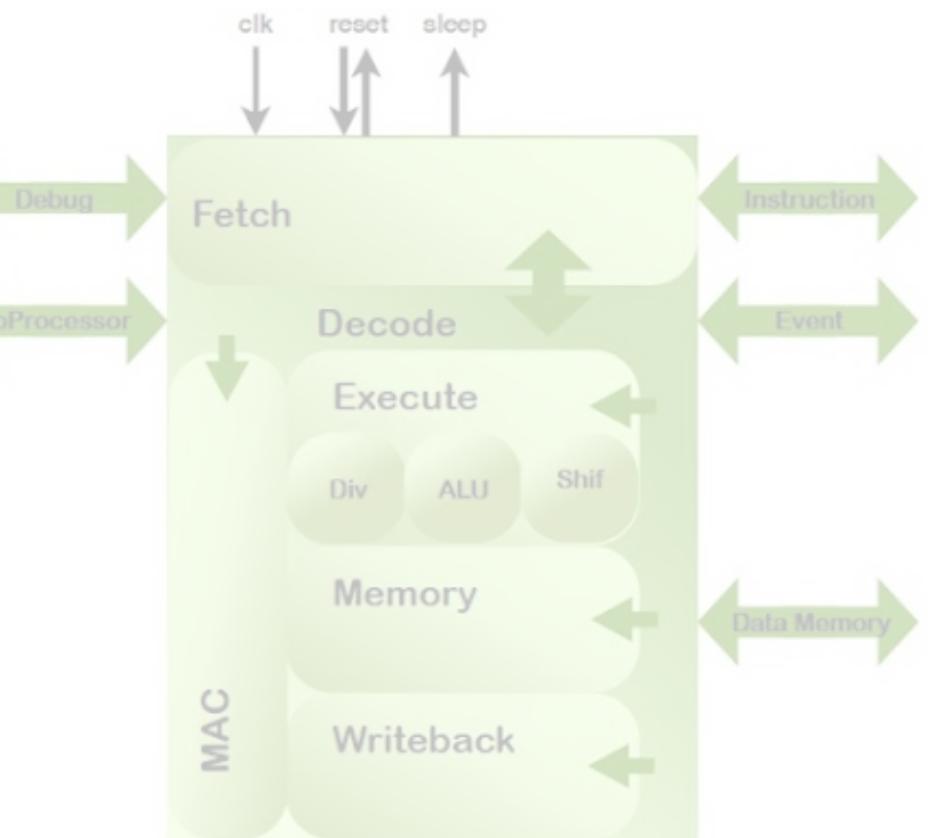

- √ J1: Simple but full 32bit machine. 30k ASIC gates. 5 stage pipeline

- √ J1sec: Trusted Compute Engine

- √ J2: Full Harvard, cache, SMP capable. 50k gates. Parallel MAC

- √ J2SMP: Linux capable Symmetric Multi-Processor

- √ J32: Virtual Memory (MMU). 100k ASIC gates

- J32FM: Multi-issue, FPU. 200k ASIC gates (target).

√ SoC Platform, Peripheral Library, SoC interconnect and top-level generators

## Why did we build it?

- J-Core is purpose built: for connected embedded systems

- Not an academic exercise: Deployed in 'Critical Infrastructure', electrical grids

- Objective: To democratize the space: When knowledge and tools are available...

- People can achieve their own goals

- Leads to Info Security, Continuity of Business, and Advancement of the Art.

- We built this so we could build products with it, and so can anyone else.

- In the end, all the way through to affordable, accessible ASIC based designs

#### Simple Application Example: VPN

- Hardware crypto accelerated VPN device for remote telework (pandemic product)

- J2SMP running Linux

- Hardware cryptographic engine, coupled to a J1 trusted compute processor

- On-SoC HSM functionality, and high speed.

- Prototype in FPGA took only a few weeks, new boards took a few months.

- ASIC path when and only if the project reaches product maturity.

# Good Techno icay (ed.) V.c. 1164. all;

- SHCompact is an excellent and solid technological foundation." (31 downto 1);

- Well researched and documented design decisions. "Unified ISA ruction\_o\_t := (en => '0')

- Multiple iterations: experience from use in real products is a second record of the second record of the second record of the second record of the second of the second

- J-Core is a clean reimplementation, in high level dialecttof VHDL

- Designed with the ESA/Gaisler '2 Process Method': std\_logic\_vector(31 downto 0); constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (constant NULL\_DATA\_0 : cpu\_data\_o\_t := (en => '0', a => (en =>

- Extensive use of code generators for the ISA and SoC bus structures

- Implemented from the ground up to do signal processing, networking

- Designed from the ground up to run Linux

```

end record;

I processing on etworking

d : std_logic_vector(31 downto 0);

rdy : std_logic;

end record;

type cpu_debug_cmd_t is (BREAK, STEP, INSERT, CONTINUE);

```

std\_logic\_vector(31 downto 0);

cion\_o\_t is record

std\_logic\_vector(31 downto 0);

type cpu\_data\_o\_t is record

## Rationale: Why go to ASIC?

- Know your devices, own your data

- Security

- Enable innovation and development, our own and in the community

#### 1. Open Source and Open Hardware

- Completely Open implementations and driving philosophy

- J-Core RTL and tools are available under appropriate Open licenses

- Hardware platforms to run it are available under open licenses

- More than just a reference design

- Complete, mature toolchains for 'bare metal' and Linux OS

- Boot code, Linux OS, Application examples...

#### HW Development Environment

- More than a development board, you can build real prototypes

- Add modules to the COTS base board. Simple interface circuitry.

- Turtle Board represents a sort of 'ideal' J-Core Embedded device platform

- 3rd party small boards like the UPDuino 2.0 useful also

### RTL, HW and SW Complete

Utils (toybox) **Network Apps User Apps** Feels like any Linux system. Bare Metal App System Libraries (Musl libc, etc) Familiar set of tools and libraries **Linux Kernel** Bootloader **Boot code, Linux port, Device Drivers FPGA** Jx CPU, SoC generator, Peripherals Hardware Platform Board Hardware Designs in EAGLE CAD

### 2. Tools and Components

- Simulate first, using GHDL and Yosys.

- Working to make the test benches more accessible

- J1 is ready to simulate and extend, right out of the GitHub Repo.

4'0000

- Scripts to build all the tools

- Might need a docker image to help folks get started

- GHDL+Yosys+NextPNR go all the way to FPGA for Lattice

# 2(3) Options for Tool Flow

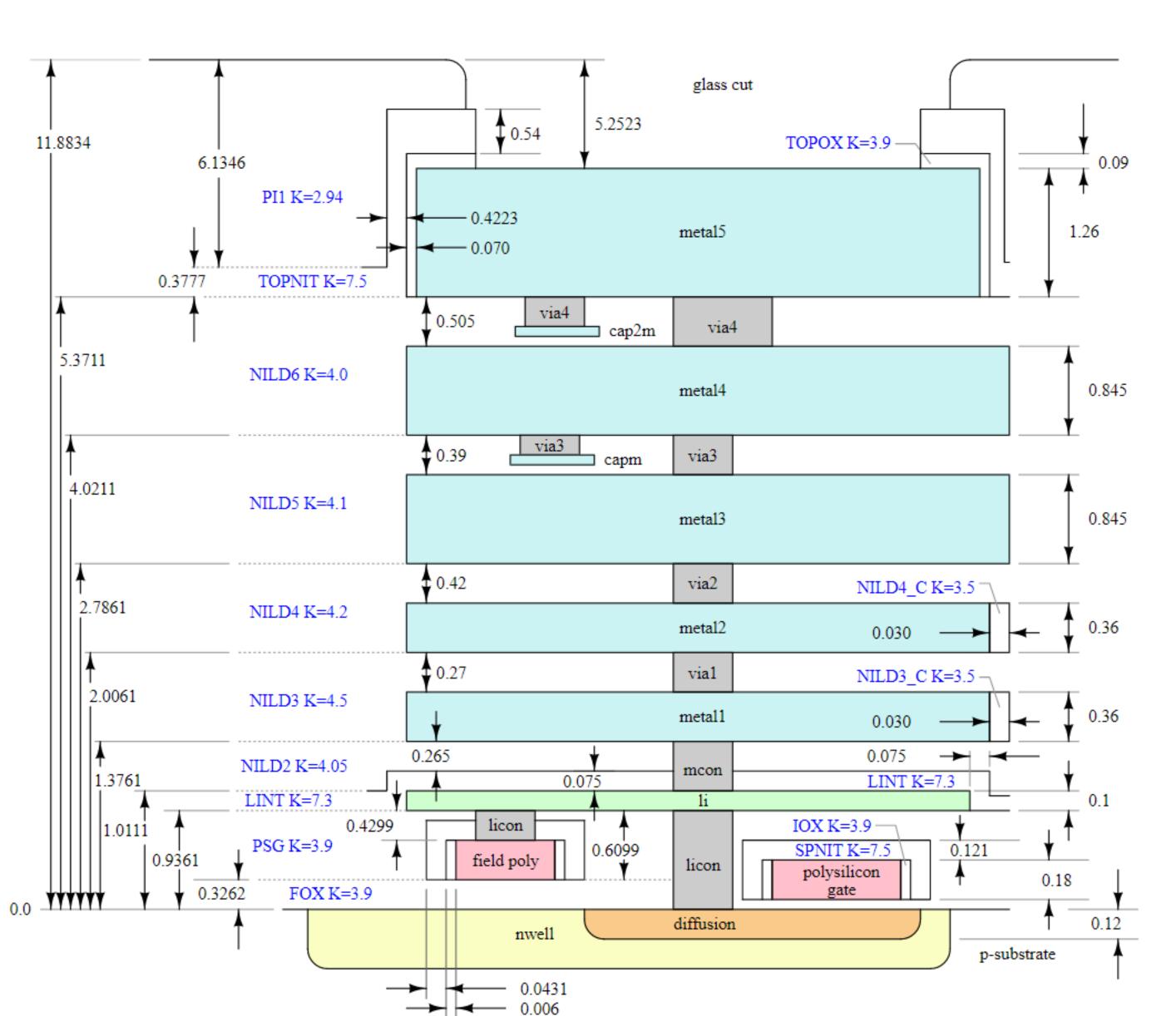

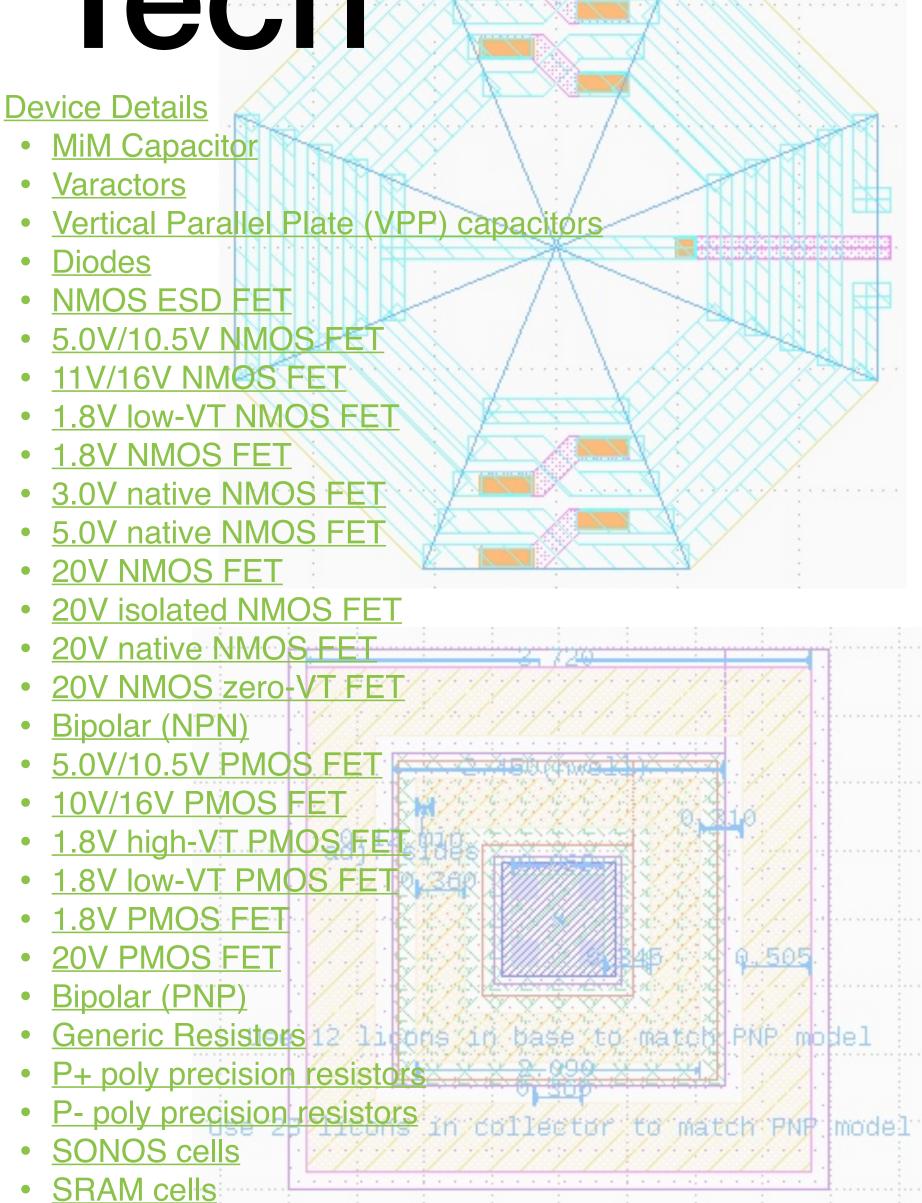

**FOSS 130nm Production PDK**

### 3. Fabrication Options

- Multiple routes:

- Older processes

- Academic and MPW service bureau access, with NDA

- New, game changing access to SkyWater 130nm mixed signal fab

# SKYWater Not Just Low Tech

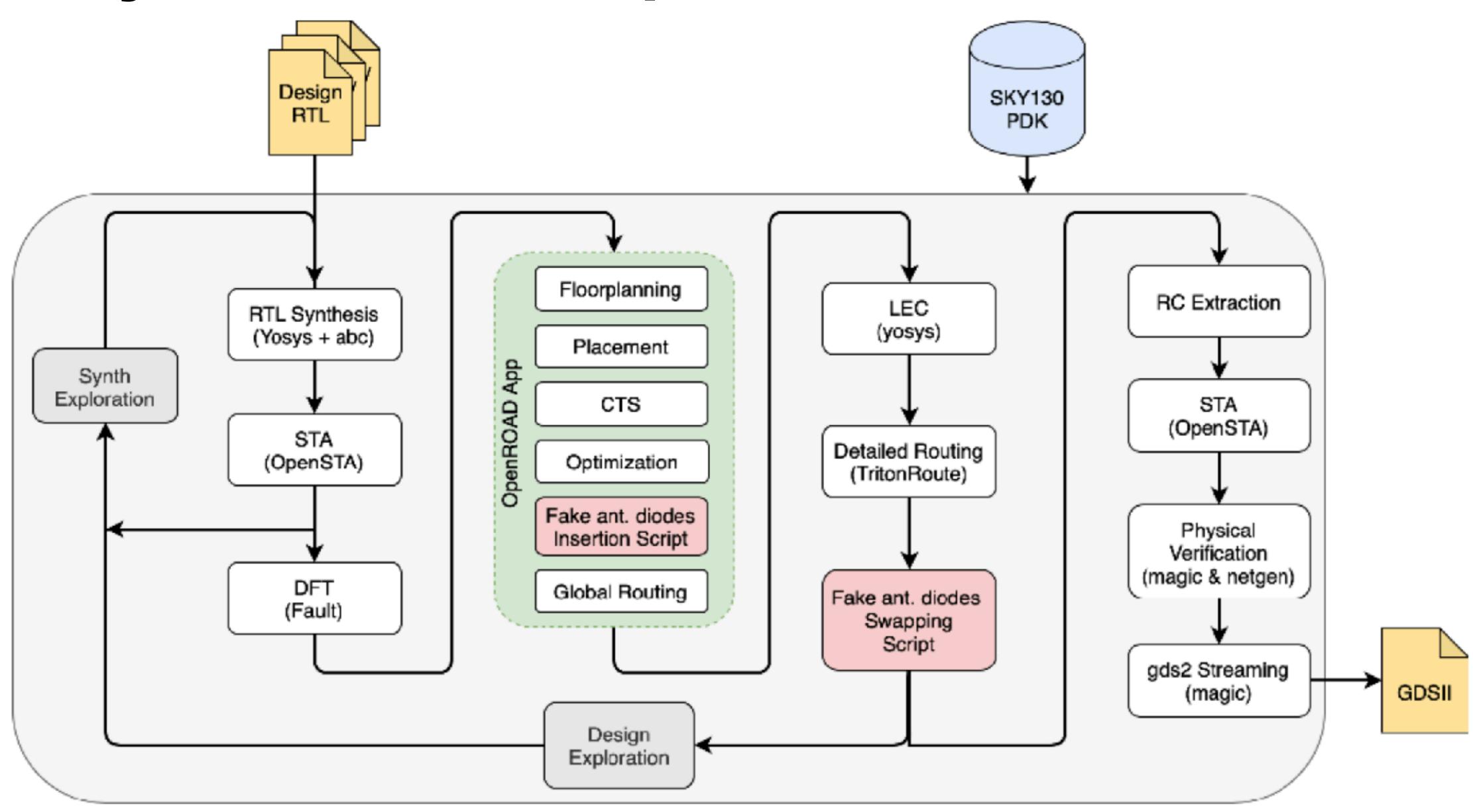

#### SkyWater130 OpenRoad Tools Flow

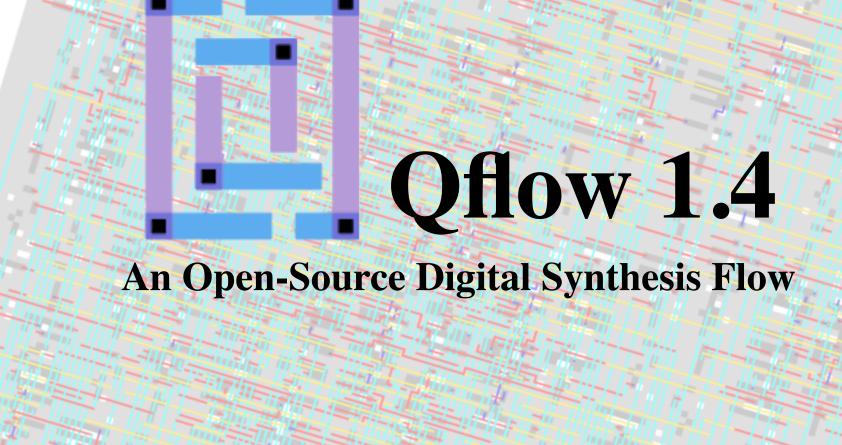

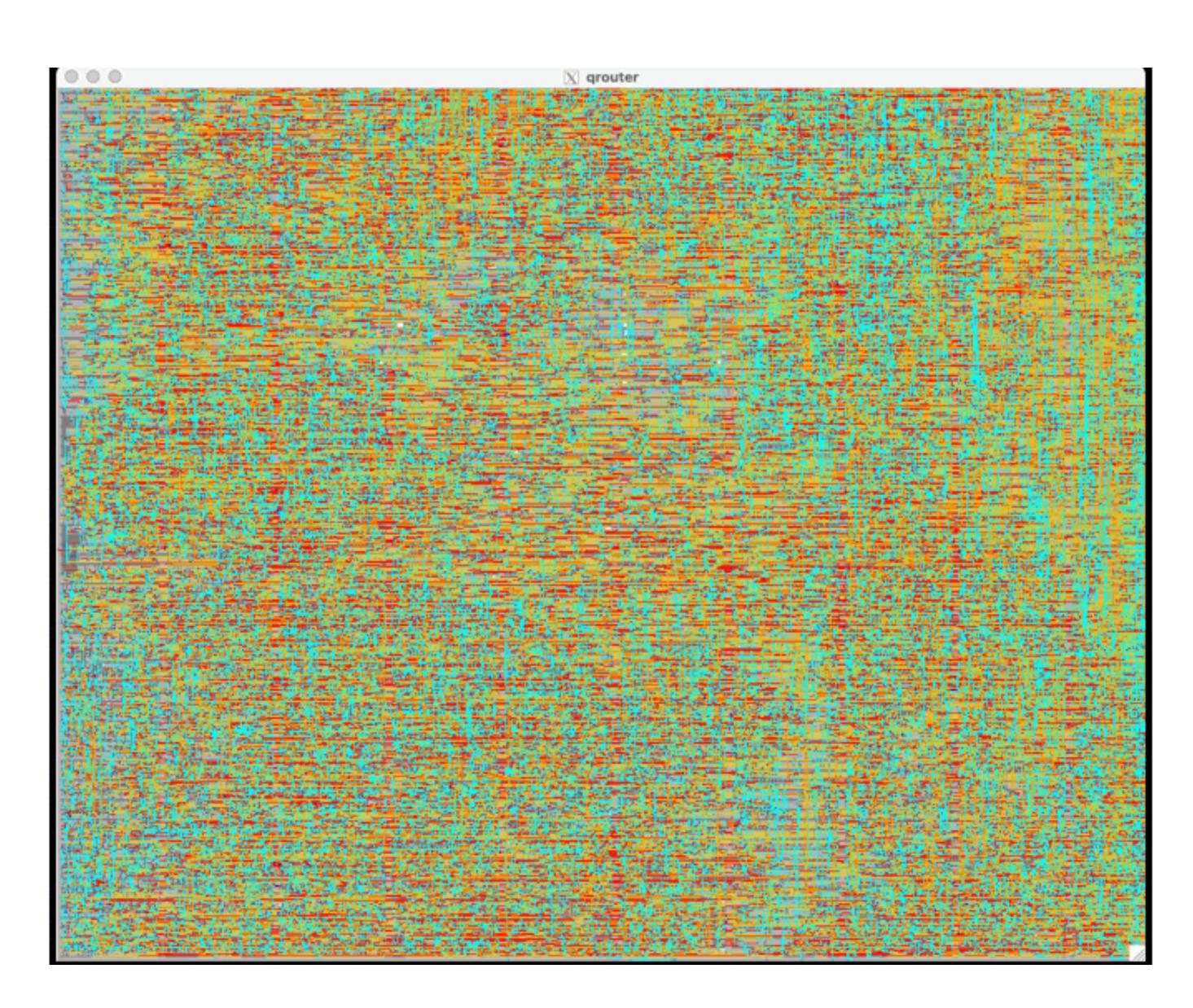

#### J1CPU 130nm QFlow Tools Place and Route

- Simple QFlow Tool Flow

- J1 CPU, first trial 492x461μm

- 0.226mm<sup>2</sup>

- SkyWater 130nm hd cells

- Proof of Concept

- Register file

### 4. Complete Design Process

- 1.Design Concept

- 2. Prototype using a standard or autogenerated SoC template

- 3. Simple interface hardware, and RTL for interface IP block

- 4. Develop and run software on the SoC in FPGA, with real interface HW

- 5. Synthesis, Place and Route with the same toolflow for standard cell ASIC

- 6. Verification and simulation

- 7. Tape out on a low cost process, hardware board design

- 8. Run proven software on new hardware with ASIC

# Questions and Wrap Up

iet the Start of the Story

Just the Start of the Story

DE EXCEPTION DEBUGI

#### Thanks

Please check out the J-Core GitHub http://github.com/j-core

QFlow and OpenPDK http://github.com/RTimothyEdwards

OpenRoad http://github.com/The-OpenROAD-Project DEBUG

FETCH

INSTRUCTION

PREFER