ELC Prague 2023

# RISC-V and Open Hardware BoF

Drew Fustini <dfustini@baylibre.com>

Baylibre

# \$ whoami

- Linux kernel developer, <u>BayLibre</u>

- embedded software consultancy based in Nice, France, with ~50 engineers around the world <u>contributing to open source projects</u> like Linux, U-Boot, Android and Zephyr

- Board of Directors, <u>BeagleBoard.org Foundation</u>

- Ambassador, <u>RISC-V International</u>

- Member, <u>FOSSi Foundation</u> and <u>Open Source Hardware Association</u>

# RISC-V: a Free and Open ISA

- Started by a computer architecture research group at University of California Berkeley in 2010 led by <u>Krste Asanovic</u>

- V as in the roman numeral five, because it is the 5th RISC instruction set to come out of UC Berkeley

- Free and Open because the <u>specifications</u> are published under an open source license: Creative Commons Attribution 4.0 International

- Volume 1, Unprivileged Spec v. 20191213 [PDF]

Volume 2, Privileged Spec v. 20211203 [PDF]

### Learn more about RISC-V

Get up-to-speed quick with the <u>RISC-V Reader</u>

### **RISC-V International**

- The organization that develops the RISC-V specifications: <u>riscv.org</u>

- Non-profit with <u>2,700+ members</u> including companies and universities

- Become a member free of cost to individuals and non-profits

- RISC-V wiki has many helpful resources

- RISC-V mailing lists for many topics (public archives)

- <u>Technical Meetings Calendar</u>

# **RISC-V Developer Boards**

- Initiative from RISC-V International to get Linux-capable boards into the hands of open source developers

- Need to be RISC-V International member (or part of a member organization), but remember that <u>individuals can join RISC-V International free of cost</u>

- Currently accepting applications for:

- Milk-V Pioneer Box featuring 64 core Sophgo SoC and 128 GB memory (!!!)

- StarFive VisionFive V2 board

# MilkV Pioneer with 64 cores!

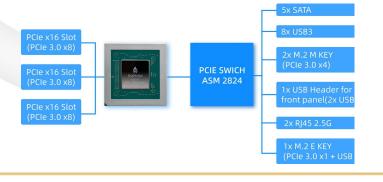

- Sophgo SOPHON SG2042 has 64-core T-Head C920 @ 2 GHz

- CrowdSupply campaign just launched, ships December 2023

- \$1,199 for Milk-V Pioneer motherboard

- \$1,999 for Milk-V Pioneer Box 128 GB ram, 1 TB SSD, 2x 10Gb Ethernet, AMD R5 230 GPU

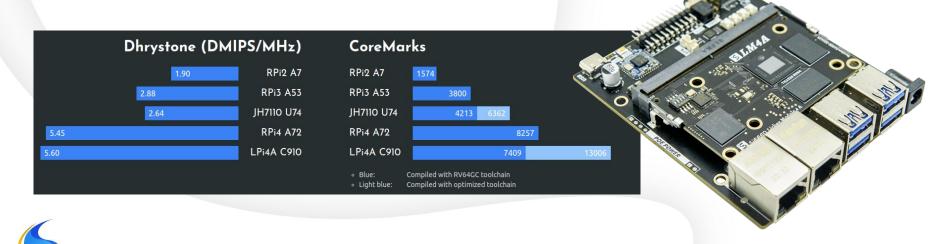

# Sipeed Lichee Pi 4A

Alibaba T-Head TH1520 SoC with 4x C910 cores (12-stage, out-of-order)

\$119 on <u>AliExpress</u>

# **Recent RISC-V presentations**

- <u>Linux on RISC-V</u> (ELC-E 2022 Dublin)

- RISC-V YouTube channel

- State of the Union & the Road Ahead

- Maturing the RISC-V Ecosystem

- <u>Evolving the Role of Software in the RISC-V Ecosystem</u>

- RISC-V Summit Europe (May 2023) videos coming soon...

# "Is RISC-V an Open Source processor?"

RISC-V is a set of <u>specifications</u> under an <u>open source license</u>

RISC-V implementations can be open source or proprietary

- Open specifications make open source implementations possible

- An open ISA makes it possible to design an open source processor

# RISC-V open source cores

- Academia

- Rocket and BOOM from Berkeley, PULP family of cores from ETH Zurich

- Industry

- OpenHW Group creating proven verified IP like their <u>Core-V</u> designs

- OpenTitan silicon root of trust project uses <u>LowRISC</u> <u>Ibex</u> core

- SweRV created by Western Digital and now developed by CHIPS Alliance

- FPGA friendly

PicoRV32, RVfpga, SERV, VexRiscV, NaxRiscv

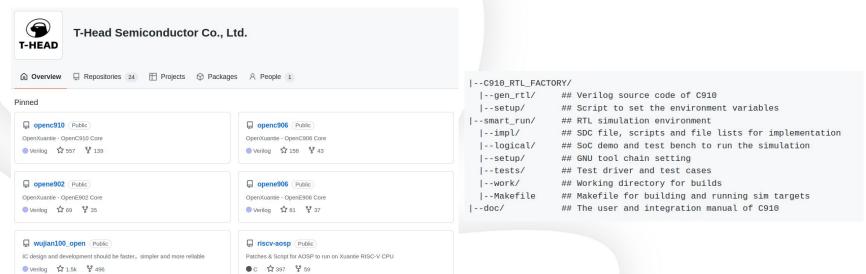

# Alibaba T-Head open source RISC-V cores

OpenE902, OpenE906, OpenC906 (used in Allwinner D1 SoC), and OpenC910 cores on GitHub under permissive Apache 2.0 licence

# XiangShan (香山)

- open source high-performance RISC-V processor project from the Chinese Academy of Science

- RISC-V Summit 2021 talk by Professor Yungang Bao (slides)

- "Contribute to XiangShan and realize your ideas on real chips! The open-source

XiangShan will be taped-out every ~6 months"

- RISC-V Summit Europe (May 2023) should be posted soon...

- Nanhu is the 2nd generation microarchitecture

o Target: 2GHz@14nm, SPEC CPU2006 20 marks; 7.81 CoreMark/MHz

# Open source silicon

- <u>FOSSi Foundation</u> (Free and Open Source Silicon)

- <u>El Correo Libre</u> monthly newsletter for the latest on open source cores

- Build your own open source SoC with an open source silicon toolchain

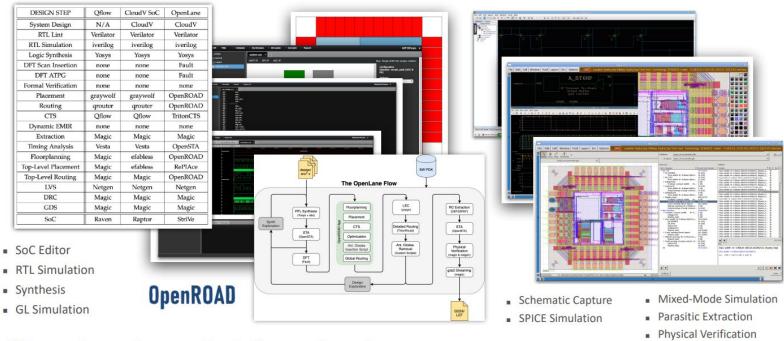

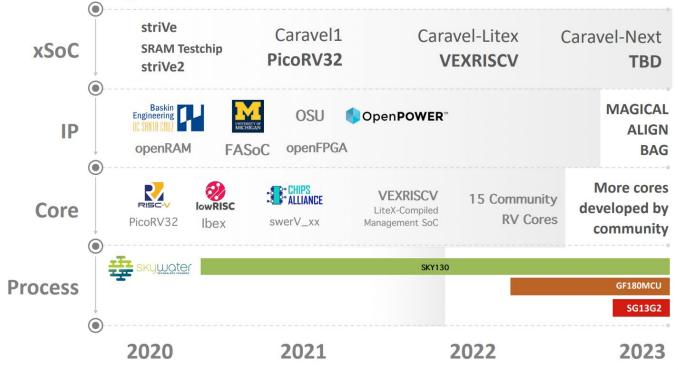

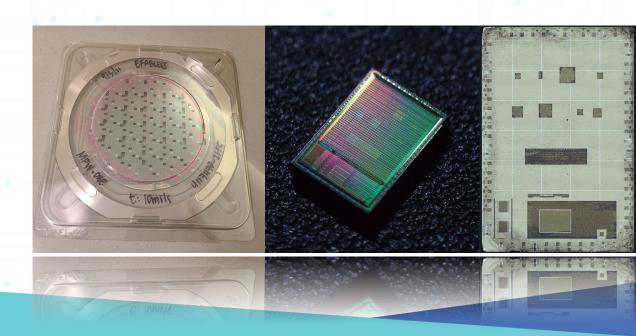

- Google and eFabless worked with Skywater to open source their 130 nm PDK (process design kit) and more recently 90 nm process; also GlobalFoundries180nm PDK too

- Google sponsored free-of-cost MPW (multi-project wafer) for open source projects

- Zero to ASIC course: learn to design your own chip using open source design tools

o <u>Tiny Tapeout</u>: design your own simple chip in <u>web browser</u> and get it made for \$100

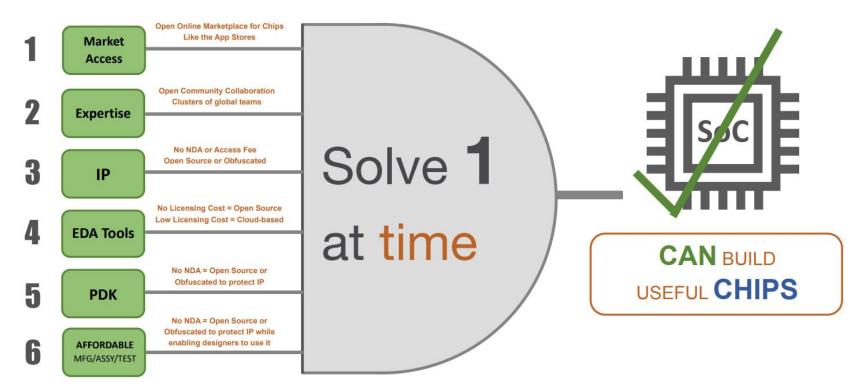

# ..... what we need ....

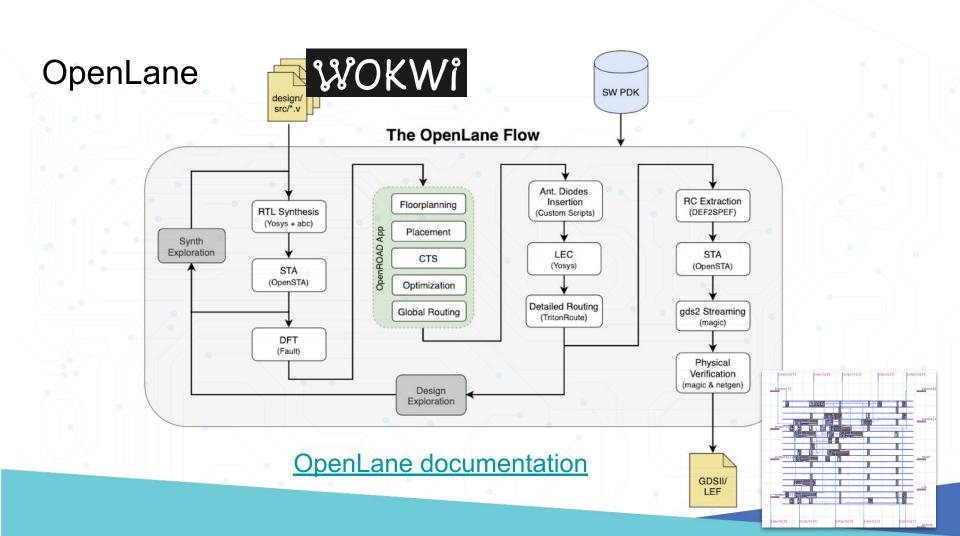

### **OPEN SOURCE DESIGN FLOWS & TOOLS**

Silicon Compiler

Coriolis

OpenLane

# A library of IP blocks - Go Build It

# Open Source technology PDKs

No NDA, nothing to sign - it's Open Source

**FOSS 180nm Production PDK** github.com/google/gf180mcu-pdk

**SG13G2 BiCMOS 0.13μm PDK** github.com/IHP-GmbH/IHP-Open-PDK

Technology PDK availability is virtually limitless Leading to massive open collaboration

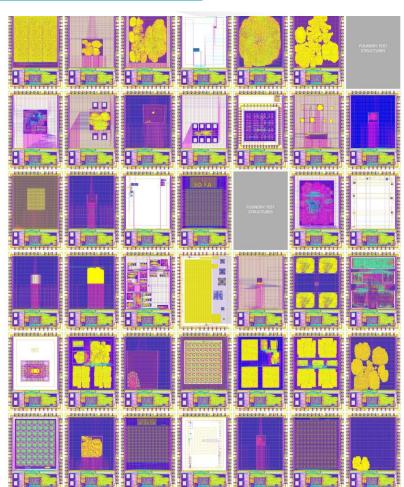

### **GOOGLE'S OPEN MPW PROGRAM**

- Google is funded 8 manufacturing runs in 2021/22

- Participants use an Harness SoC (<u>Caravel</u>) with 10mm2 open area

- SKY130 Open Source Digital & Analog Design Tools are available

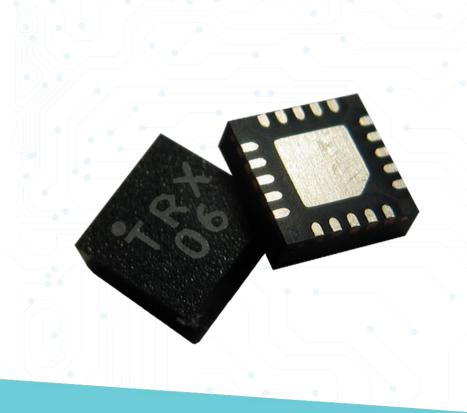

- Participants get 5 dev boards + 300 WCSP-packaged parts

- All designs must be public and under an open source license

- All designs must contain information & files to reproduce the work

- Participants are strongly encouraged to try new ideas, take risks and iterate

- All skill and experience levels are welcome to participate

Start here <a href="https://ef.link/gmpw">https://ef.link/gmpw</a>

First MPW

Overbooked

45/40

45 designs submitted in 30 days!

All designs must be **Open Source**

### **DESIGN TYPES**

- 9 x Open processor cores

- 9 x SoC's

- Crypto-currency Miner

- Robotic App Processor

- Amateur Satellite Radio Transceiver

- 7 x Analog/RF

- 5 eFPGA's

### **COMPANIES**

- IBM: OpenPOWER -MicroWatt

- QuickLogic eFPGA

- Antmicro

- Western Digital Swerv-EL2

- EFabless

- SpinMemory

- Design using SkyWater SKY130 (130nm) rich process + std cells + IO cells

- Start from the Caravel Harness no cost book your slot for \$200

- You <u>choose your licensing terms</u> for your design by <u>default it's proprietary</u>

- The offered area (10mm2) is not just silicon area It is a framed house with plumbing and electricity just bring your appliances

- Cycle Time 95 days +/- depending on the package choice

| Rapid Prototyping     | \$9,750  | 100 QFN parts + 5 dev boards   | $\bigcup$ |

|-----------------------|----------|--------------------------------|-----------|

| Engineering Samples   | \$9,750  | 300 WCSP parts + 5 dev boards  |           |

| Low Volume Production | \$20,000 | 1000 WCSP parts + 5 dev boards |           |

# New & Different Type of Users

1/3

self-identity

software devs!

60% first time designers!

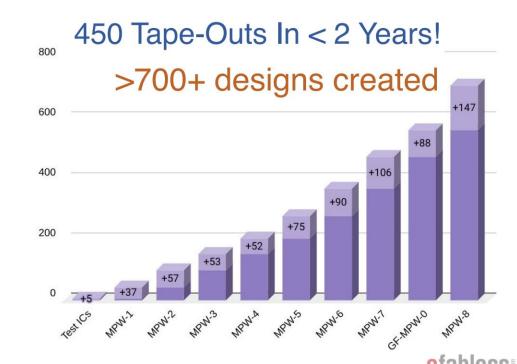

# Open Source Designs - Explosive Growth

April 2021 to Date

Fastest Ever Design

Creation Rate

Sponsored By:

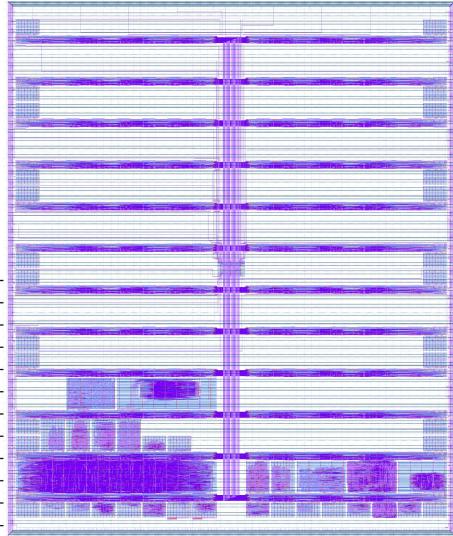

## MPW-2 Working Silicon – "Yi-Five"

32-bit RISC-V Core with SDRAM Memory Controller and Quad SPI

@dineshannayya SoC designer from Intel

Booting Phase

USER PROJECT

STORY OF THE ST

"Being in this VLSI industry for more than 20+ years, I never thought that in my lifetime I would be able to demonstrate my skills from home, develop a 100K+ gate count VLSI design using open source tools, and get it fabricated for free with working silicon. It's a dream come true."

### MPW-2 Working Silicon – "FABulous"

Custom FPGA fabric of 896 LUT4s, 64 LUT5s, 8 DSPs and 8KB of BRAMs

"With the MPW2 silicon back and provided harness, we were able to obtain our first silicon results from the FABulous eFPGA fabric generator. This included building a demo that tests all the fabric features - not just LUTs and FFs but also DSPs and BRAM."

### @gatecat

Student at Heidelberg University and FOSS FPGA tool maintainer

# BONUS: Tiny Tapeout slides from Matt Venn <a href="https://bit.ly/tt-ws-slides">https://bit.ly/tt-ws-slides</a>

# Tiny Tapeout 4 From idea to chip design in minutes!

### Try the interactive version

### Try the interactive version

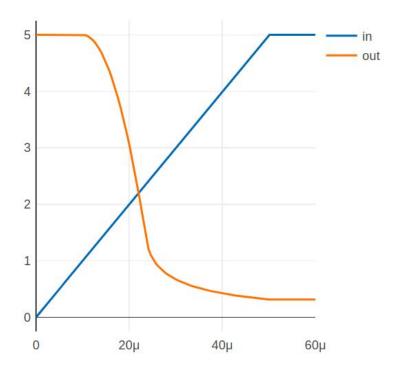

Plot signals:

in 🔕

out 🛚

3)

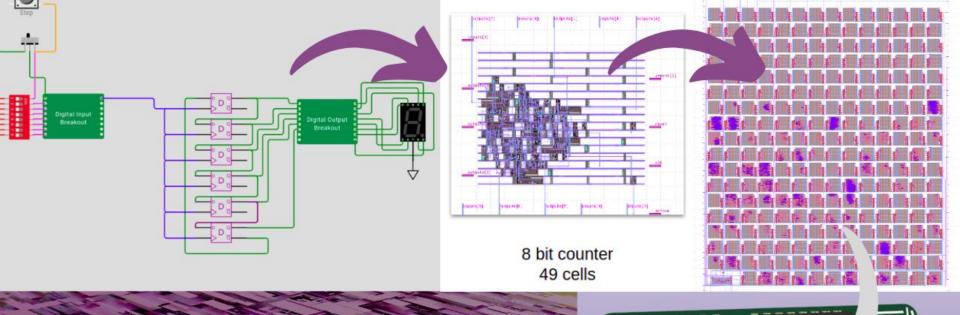

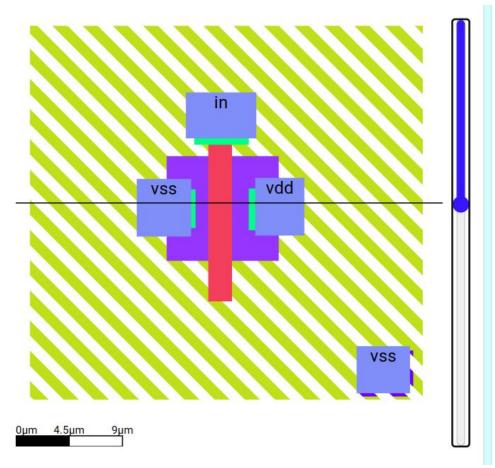

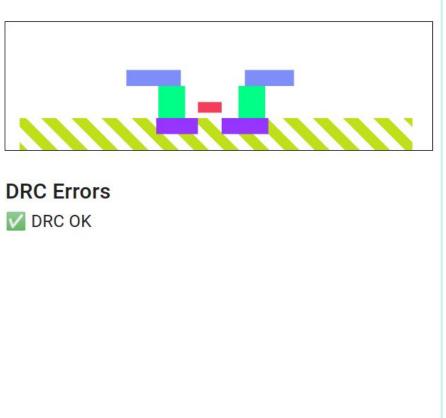

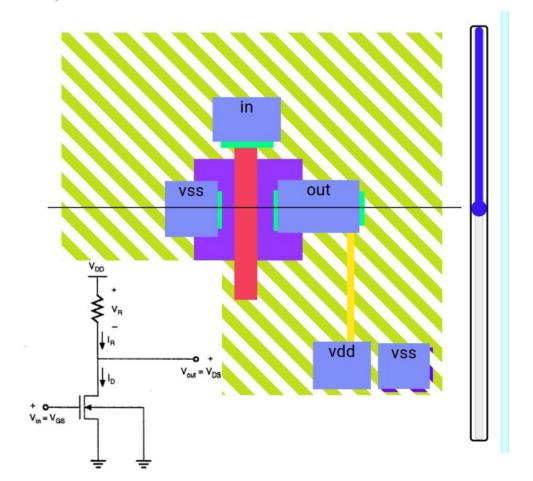

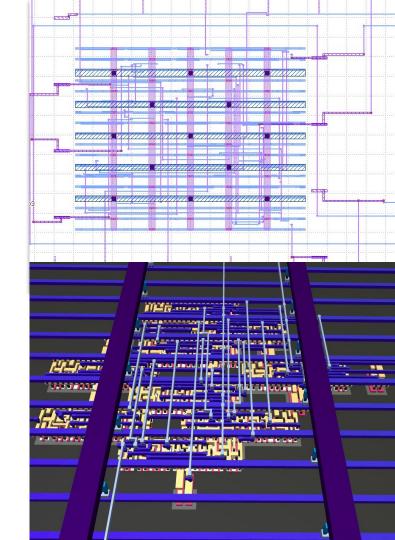

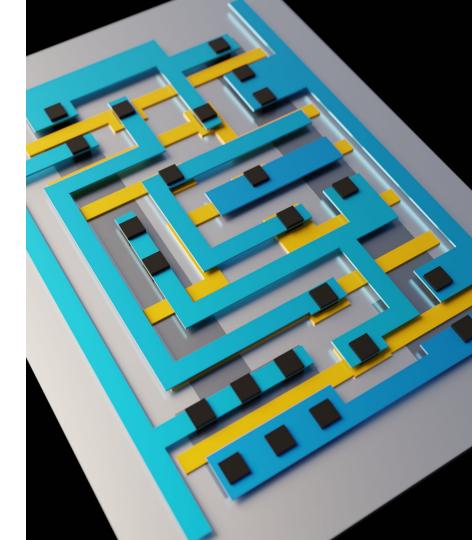

### HDL -> GDS

- Create new Github project by forking template

- Update config to fetch your design from Wokwi / use an HDL

- Github action builds the GDS

- 160 x 100 um size

- enough for about 1000 gates

- 10 ins, 8 outs, 8 bidirectional

- No tool install or download

- Easy to share image of your design

- 3D viewer / explorer

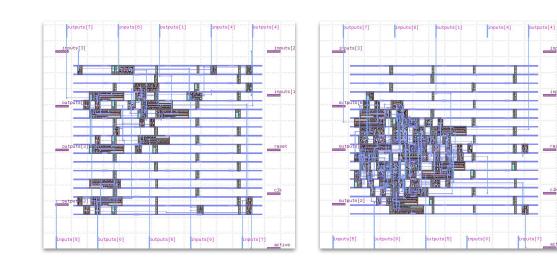

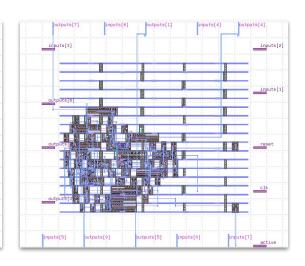

# GDS examples (all 70um x 70um)

binary to decimal converter 25 cells

8 bit counter 49 cells

inputs[2]

4 bit counter & bcd 50 cells

# Optional - pay for your design to be manufactured!

- \$100: IC + PCB

- \$50: your design on the IC but no chip or PCB

**Example** School runs workshop for 10 people and orders 1 board:

- $\bullet$  9 x \$50 + 1 x \$100 = \$550

- \$550 / 10 participants = \$55 per ticket

# Tiny Tapeout stats

| Run  | Launched   | Closed     | Shuttle | Designs                      |

|------|------------|------------|---------|------------------------------|

| TTO1 | 2022-08-17 | 2022-09-01 | MPW7    | 152                          |

| TT02 | 2022-11-09 | 2022-12-02 | 2211Q   | 165                          |

| TT03 | 2023-03-01 | 2023-04-23 | 2304C   | 249 (includes 149 from TT02) |

# Add new designs

- GDS generation done with GH action

- High speed IO ~50MHz

- Supports around 300 designs

- Multi tile support

- TT04 will tapeout September 202

- Submission template

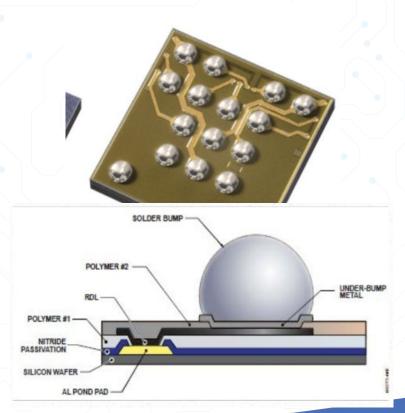

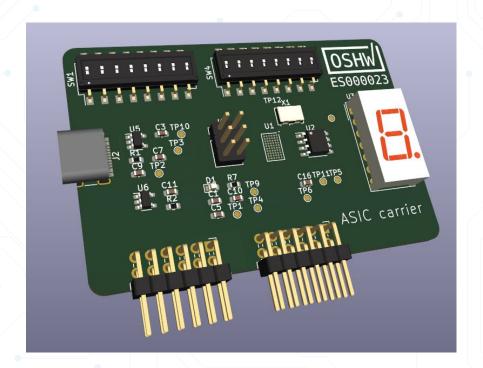

# Packaging: QFN or Wafer Level Chip Scale Package

#### Receive PCB with custom chip mounted

- USB C psu, 3.3v and 1.8v

- Adjustable clock / single step

- 9 dip for design select (or jumpers)

- 8 dip for inputs

- 8 leds for outputs

- Include PMOD headers / mount holes

#### Receive emails throughout the ~6 month wait

- ASIC basics / tutorials / ideas for designs / this week's coolest design

- Virtual factory tour

- Wafers out

- Testing

- PCBs out

- PCBs sent

#### Connect with me

- Slides <a href="https://bit.ly/tt-ws-slides">https://bit.ly/tt-ws-slides</a>

- Newsletter

- Youtube channel

- Twitter <u>@matthewvenn</u>

- Linked.in

- Take my full <u>course</u>

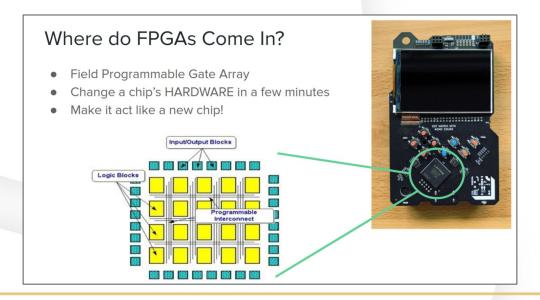

# BONUS: What about RISC-V on FPGAs?

#### Introduction

"RISC-V and FPGAs: Open Source Hardware Hacking" keynote at Hackaday Supercon 2019 by Dr. Megan Wachs

## Open source FPGA toolchains

- Project IceStorm for Lattice iCE40 FPGA

- Project Trellis for the more capable Lattice ECP5 FPGA

- Project X-Ray for the much more capable Xilinix Series 7

- <u>F4PGA</u> (formerly SymbifFlow):

- "F4PGA is a fully open source toolchain for the development of FPGAs of multiple vendors. Currently, it targets the Xilinx 7-Series, Lattice iCE40, Lattice ECP5 FPGAs, QuickLogic EOS S3 and is gradually being expanded to provide a comprehensive end-to-end FPGA synthesis flow."

## Why design an SoC in Python?

- Python has advantages over traditional HDL like VHDL and Verilog

- Many people are familiar with Python than HDL (hardware description languages)

- Migen\* is a Python framework that helps automate chip design

- Leverages the object-oriented, modular nature of Python

- Produces Verilog code so it can be used with existing chip design workflows

- \*Amaranth is the future. Formerly called nMigen which was itself a rewrite of Migen.

- Myrtle "gatecat" Shah of ChipFlow: <u>Building SoCs with Python and Open Tools</u>

#### What is Migen?

```

library ieee;

use ieee.std_logic_1164.all;

entity my_module is

clk : in std_logic;

o : out std_logic

end entity;

architecture rtl of my_module is

signal d : std_logic;

signal q : std_logic;

o <= q;

d <= not q;

process(clk)

if rising_edge(clk) then

d \leftarrow a

end if;

VHDL

end rtl;

```

```

from migen import *

class MyModule(Module):

def __init__(self):

self.o = Signal()

d = Signal()

q = Signal()

self.comb += [

self.o.eq(q),

d.eq(~q)

self.sync += d.eq(q)

Migen

```

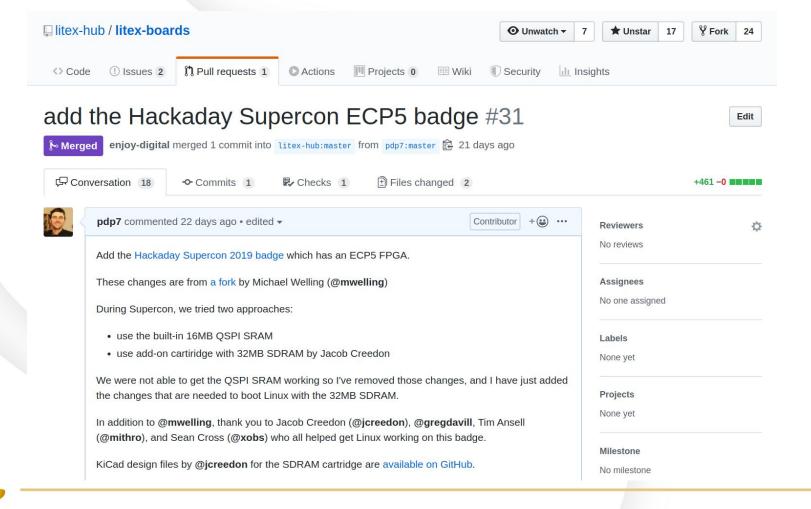

Enjoy Digital

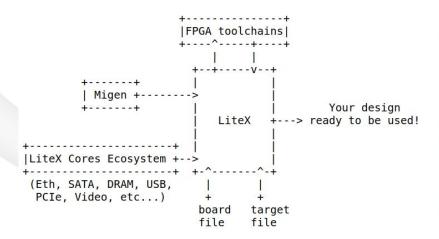

## **LiteX**

- Based on Migen, builds full SoC that can be loaded into an FPGA

- Collection of open cores for DRAM, Ethernet, PCIe, SATA and more...

| Name         | <b>Build Status</b> | Description              |

|--------------|---------------------|--------------------------|

| LiteX-Boards | ci passing          | Boards support           |

| LiteDRAM     | () ci passing       | DRAM                     |

| LiteEth      | ( ci passing        | Ethernet                 |

| LitePCIe     | ( ci passing        | PCIe                     |

| LiteSATA     | ci passing          | SATA                     |

| LiteSDCard   | ( ci passing        | SD card                  |

| LitelCLink   | () ci passing       | Inter-Chip communication |

| LiteJESD204B | ( ci passing        | JESD204B                 |

| LiteSPI      | ci passing          | SPI/SPI-Flash            |

| LiteScope    | n ci passing        | Logic analyzer           |

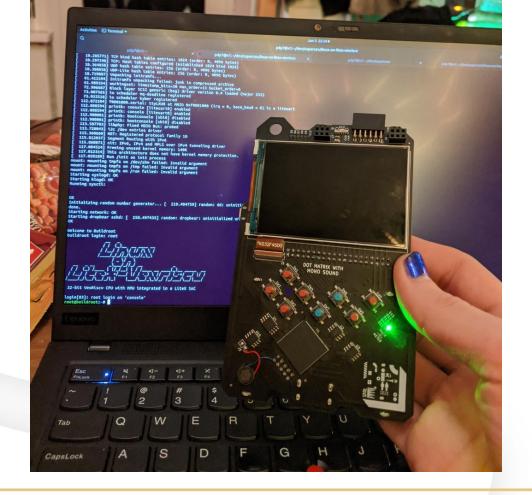

### **Linux on LiteX-VexRiscy**

- <u>VexRiscv</u>: 32-bit Linux-capable RISC-V core

- Designed to be FPGA friendly

- Written in Spinal HDL (based on Scala)

- Builds an SoC using VexRiscv core and LiteX modules

- Such as LiteDRAM, LiteEth, LiteSDCard, LitePCle

- o "This project demonstrates how high level HDLs (Spinal HDL, Migen) enable new possibilities and complement each other. Results shown here are the results of a productive collaboration between open-source communities"

- Supports large number of FPGA dev boards including Digilent Arty A7

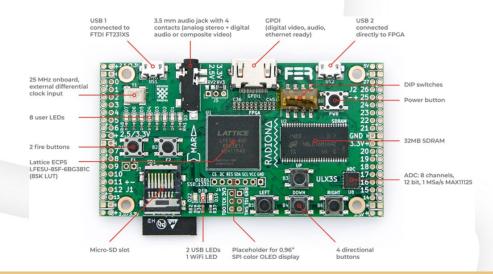

## Open Source ECP5 FPGA boards

- Radiona.org ULX3S

- 32MB SDRAM; ESP32 on-board for WiFi and Bluetooth; \$115 on <u>CrowdSupply</u> or <u>Mouser</u>

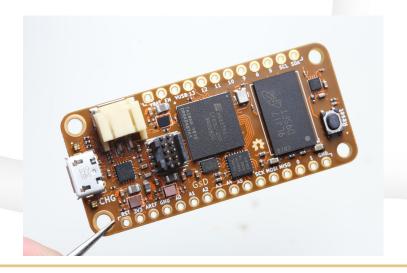

# Open Source ECP5 FPGA boards

- OrangeCrab by Greg Davill

- 128MB DDR RAM; Adafruit Feather form factor; available for \$129

## Want to learn FPGAs? Try Fomu!

- Online workshop from Tim Ansell and Sean Cross

- \$50 on CrowdSupply

- Fits inside USB port!

- Learn how to use:

- MicroPython

- Verilog

LiteX