# Using Interrupt Threads to Prioritize Interrupts

Aren't Interrupts the Highest Priority Already?

Mike Anderson Chief Scientist The PTR Group, Inc.

mailto: mike@theptrgroup.com

http://www.theptrgroup.com

#### What We Will Talk About

- ₩What is latency?

- **★**Sources of latency in real-time systems

- ★Misconceptions about interrupt service routines

- ★Executing interrupt code in a thread context

- **₩**Interrupt threads in Linux

- **★**Some notional performance comparisons

- **₩**Summary

Threads CELF 6FO-

Consider (c) 2010. The PTRGrain To

#### A Definition of Latency

- \*Latency can best be described as the difference in time between when an event is signaled and when code starts to run

- ★Operating systems have:

- Scheduling latency

- ▶ Interrupt latency

- And more...

- ★Because we deal with the real world, we must deal with latency

- ▶ The real world is not a very deterministic place

Inff Iweads-CELF-6FO

opyright (c) 2010, The PTRGroup, Inc.

# Scheduling Latency

- ★Scheduling latency is the amount of time between when a high-priority thread becomes ready to run and when it gets the CPU

- **★**Affected by:

- Disabling the scheduler

- E.g., the BKL in Linux or taskLock() in VxWorks™

- Non-preemptible system calls

off wards CRE 580.

Consists (c) 2010. The PTBGroup Ti

#### Interrupt Latency

★The amount of time between when an interrupt is signaled and when the ISR begins to execute

#### ★Affected by:

- ▶ Long-duration ISRs

- Disabling interrupts

- ▶ The order of interrupt arrival

Infilmeds-CBF-6F0

Copyright (c) 2010, The PTRGroup, Inc

#### Taxonomy

#### ★Deterministic execution

- This means that code takes the same amount of time to run every time

- The holy grail of real-time systems

#### ★Real-time computing

▶ Computing with a deadline

#### ★Soft real time

- Deadlines are squishy

- Executing after the deadline has diminishing value

- **⊁**Hard real time

- If you miss the deadline, people get hurt or data is lost permanently

Inff Iweads CELF 6F

Consider (c) 2010. The PTRGrain To

#### Real-time isn't Fair

- ★Embedded RTOS developers know that realtime applications are decidedly unfair

- Time slicing may or may not exist in your RTOS

- ★In fact, many RTOSes don't support roundrobin scheduling very well

- Preemptive, priority-based is the scheduler of choice

That's SCHED\_FIFO to us Linux folks

- ★This unfairness requires a different mindset from traditional desktop development

- ▶ Can take some getting used to

ndf heads CELF-SFO-7 Copyright (c) 2010, The PTRGroup, Inc

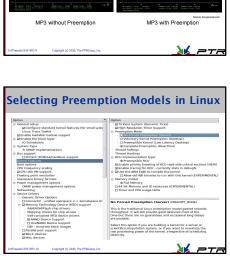

## Preemption in the O/S Kernel

- ★Ideally, an embedded O/S kernel should be fully preemptible

- Being fully preemptible enables the most responsiveness to high-priority code

- Unfortunately, it may also reduce throughput

- ★Not all kernels are fully preemptible

Early Linux was a good example of this

- Nearly all kernels have some regions of non preemptibility

- Semaphore operations, memory allocation, ISR dispatch, etc.

- The number and duration of these regions will impact responsiveness

Threads CELF 6F0

Consists (d. 2010, The PTBGroup, In

# Preemption Latency is Key

- **★**So, why the emphasis on task preemption latency?

- If we run our ISRs in threads, we need to know how long before they can run

- ★The more responsive the kernel, the more responsive our interrupt threads

- ★Long duration, non-preemptible system calls will kill our performance with the techniques we'll discuss

rff heads-CELF-6FO-11

Copyright (c) 2010, The PTRGroup, Inc.

#### **Prioritizing Interrupts**

- ¥For most of us, ISRs represent the highest priority entity in our system

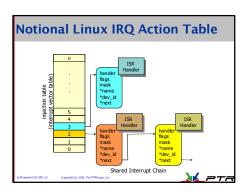

- ★The venerable VMEbus supported an interrupt hierarchy

- Int 5 could preempt Int 4 but not Int 6

- ★Unfortunately, PCI bus doesn't support interrupt priorities

- Any interrupt can preempt any other interrupt

- Interrupt sharing can make interrupt chains incredibly long running

- ★We'd like to be able to prioritize PCI interrupts as well

off Iweads CELF-SFO-1

wavishe (c) 2010. The PTRGroup To

# **Breaking Training**

- ★We've been trained to think that interrupt code must be:

- ▶ Fast

- ▶ Atomic

- Run in a special context

- ★But, what processor instructions \*must\* be run in interrupt context?

- Return from interrupt

- . E.g., PPC RFI or x86 IRET

- ▶ That's about it

- **★**OK, what about fast and atomic?

#TheadsCFIE-890-14 Consider (4 2000 The PTRGman

aurox sportirnéde

## How Fast is Fast Enough?

- ₩ Well, it depends...

- Do we have a buffer that will be overrun?

- When does the hardware interrupt get reenabled?

- ▶ Buffering may be automatic and in hardware

- ★ If we have to re-arm the interrupt in our ISR, then it's likely that the re-arm can wait until we get to it

- ➤ Will data be lost? Is it important?

\*\*Georgist (c) 2008, The PTRGraup, Inc.\*\*

# OK, How about Atomic?

- Many O/Ses support the concept of nested interrupts

- E.g., interrupts masked at the PIC rather than at the CPU itself

- Our interrupt stack must handle worst case nesting

- By their nature, nested interrupts are not atomic

- I could be in the middle of an ISR and get interrupted by another interrupt

- ★ It's likely important to prioritize interrupts

- We may want highest priority interrupt to run to completion

- ▶ Especially true for mission-critical systems

InfluenceREARO.II

Consists (4) 2010. The PTRGrain To

# **ISR Latency Sources**

- ★The most significant ISR latencies come from two sources

- Disabling interrupts in driver or user code

- E.g., local\_irq\_disable()/local\_irq\_enable() in Linux

- Performing non-deterministic operations in the ISR itself

- E.g., copying packets from network hardware during the ISR

- ★A common technique is to separate the code which must be done immediately from the code that is non-deterministic

- ▶ Known as top-half/bottom-half approach

Inff Iwads-CELF-SPO-17

Copyright (c) 2010, The PTRGroup, Inc.

# Top vs. Bottom Half

- ★The goal of this approach is to make the top half deterministic

- Maybe just acknowledge the IRQ and then schedule post-interrupt work

E.g., A tasklet in Linux

- The bottom half runs in a different context

- The interrupts are re-enabled

- Lengthy copy operations are moved here

- Rearming the IRQ is the last thing you do

- ★The bottom half is usually dispatched as a software ISR

- ▶ Little or no ability to prioritize

Decade CRE-680-18 Consider (A 2010 The PTROmen To

#### Interrupt Latency Reduction

- ★We've learned to use bottom halves to reduce interrupt latency

- Lengthy copy operations can be moved to SoftIRQ/tasklet/work queue to re-enable interrupts while the copy proceeds

- ★Work queues are kernel threads

- ▶ They're scheduled, have priorities and can sleep

- ★The ISR top half can be a single schedule\_work() call

- This makes the top half deterministic

Inff Iwads-CELF-8FO-19

Copyright (c) 2010, The PTRGroup, Inc.

## **Scheduling Work**

- ★ The Linux scheduler is O(1)

- Deterministic dispatch time

- ★ This means that the work queue will be scheduled in constant time

- ★ Since the work queue is a thread, it can run as long as needed (SCHED\_FIFO)

▶ Highest priority wins with the scheduler

- ★ This means we can use R-T priorities to prioritize execution of bottom half

- This is something we didn't have with tasklets/softIRQs

| View |

Source inhants on

InfluenceREARO.20

Consists (c) 2000. The PTRGrain To

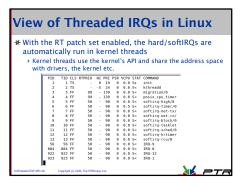

#### R-T Patch to the Rescue

- ★What the R-T patch does is to institutionalize the work queue idea

- All hardIRQs and softIRQs execute in high-priority kernel threads

- ★Threaded hard and soft IRQs can be disabled via kernel command line or in /proc

- ▶ hardirq-preempt=0/1

- /proc/sys/kernel/hardirq\_preemption

- ▶ Similar options for softIRQs

Inff heads CELF 8FO-2

Copyright (c) 2010, The PTRGroup, Inc.

Source incredinating a

#### Threads are Created Automatically

- ¥You don't have to do anything special to run your code in a thread

- request\_irq() call creates the thread and includes your function

if (!(new->flags & IRQF\_NODELAY))

if (start irq thread(irq, desc))

return -ENOMEM;

- ★This code will pass your ISR to the start\_irq\_thread function

- Creates a kernel thread that calls your ISR code

Theads CREARO.

wastelf (c) 2010. The PTBGreen 1

## The start\_irq\_thread Call

#### Prioritizing Interrupts w/ Interrupt Threads

- ★ We associate each ISR with a unique thread

- Each thread has its own priority

- Threads of the same priority will run back-toback in the order they were scheduled

- By keeping the ISR short (just schedule the thread), we make ISR top halves deterministic

- The deterministic scheduler then schedules the highest priority thread

- Hardware IRQ prioritization is a side effect

- This means that interrupt thread dispatch is deterministic

- What you do in the thread doesn't have to be

- Only another ISR or higher priority thread will preempt you

- This is what we want anyway

dThreads-CELF-SPO-24 Copyright (c) 2010, The PTRGroup, Inc.

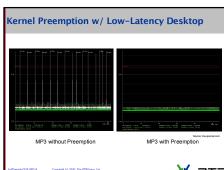

# Reduction of Jitter due to Latency \*Here is an example of latency reduction due to the use of interrupt threads \*Difference between the green and blue lines is the use of ISR threads

#### Not Every ISR Should be Threaded

- ★ You do not have to thread all your ISRs

- Just because you can doesn't mean you should

- ★ There are some classes of ISRs where this approach doesn't make sense

- ▶ Timer ISRs

- ISRs that are already deterministic like receiving on a serial port

- The overhead of scheduling exceeds their nominal run time

- ★ Just try to make sure that everything is as deterministic as possible

- Make sure that you measure it afterwards to verify you actually improved responsiveness

Inff heads CELF 6FO-2

Copyright (c) 2010, The PTRGroup, Inc.

#### Deterministic may not be Faster

- \*Because of the issues of preemption and the overhead of running the scheduler, interrupt threads may not be faster than the old approach

- It's deterministic, but not faster

- ★A good trade for some applications

A bad one for others

- ★That's why you need to use interrupt threads only where they make sense

- ★Interrupt reduction techniques may also be important

- Don't immediately re-enable the IRQ in the bottom

- Poll the device instead to avoid overhead of servicing IRQ and rescheduling

Threads CELF 6FO -

Copyright (c) 2010, The PTRGroup, Inc.

#### **Summary**

- \*Real-time means being fast enough

- Determinism is nice to have when you can get it

- · Some applications, like audio, require it

- ★The use of interrupt threads enables developers to prioritize interrupts and make interrupt servicing more deterministic

- Jitter goes way down

- May require some system redesign to take full advantage of threading

- **★**Use interrupt threads judiciously

- Not every ISR needs this approach

ff heads CELF 6FO-29 Copyright (c) 2